Programmation et programmateur ispLSI de Lattice

Une question, un problème ou une suggestion, n'hésitez pas : un petit mail

But

Programmer ce type de composant (ici in ispLSI1016 de Lattice) puis le tester sur une carte d'expérimentation.

Logiciel

J'ai uilisé l'outil ispLEVER fourni par Lattice.

Après le choix du composant, on inclut le programme source ici un fichier Abel.

Vous trouverez ici (11 ko) tous les fichiers de ce projet.

Source

La fenêtre d'édition du fichier Abel avec le programme de test utilisé ici, un diviseur numérique par 2, 4, 8, 10, 20 et 40.Cela permet de générer du 20MHz, 10 MHz, 5 MHz, 4 MHz, 2 MHz et 1 MHz à partir d'une horloge à 40 MHz.

Source

La définition des pins utilisées par le "Constraints Editor".

Simulation

Visualisation des vecteurs de test.

Programmation

Vous trouverez facilement sur le site de Lattice le schéma du programmateur connectable à une interface PC parallèle.

Ici racordé à une petite interface pour une plaque de prototypage Labdec.

Programmation

Fenêtre de paramétrage de l'outil de programmation ispVM de Lattice.

L'adresse bizarre vient de l'utilisation d'une carte PCMCIA sur mon portable.

Test

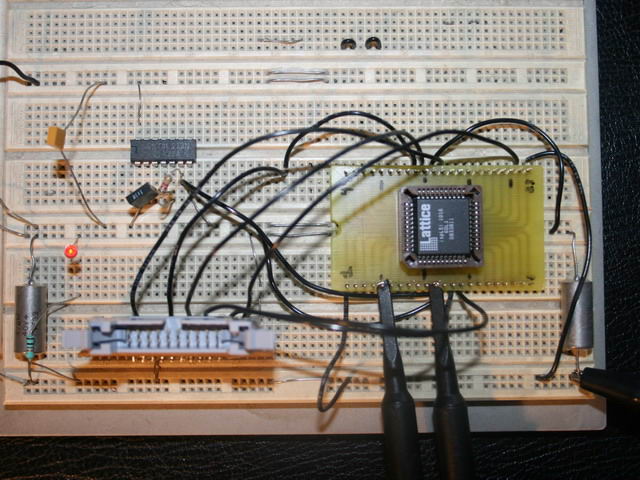

Le montage de test réalisé sur une Labdec en utilisant un adaptateur PLCC 44.

Test

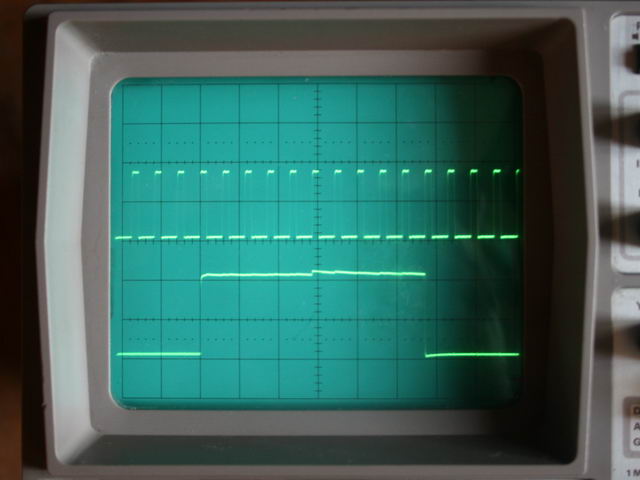

Résultat au scope de l'entrée d'horloge (en haut) et la sortie divisée par 20 (en bas).