Lattice ispLSI programming and programmer

A question, a problem or a suggestion, don't hesitate : a little email

Aim

Program this kind of component (here an ispLSI1016 from Lattice) and test it on a breadboard.

Software

I have used the ispLEVER tool from Lattice.

After the choice of the component, just include the source file, here an Abel file.

You will find here (11 ko) all the files for this project.

Source

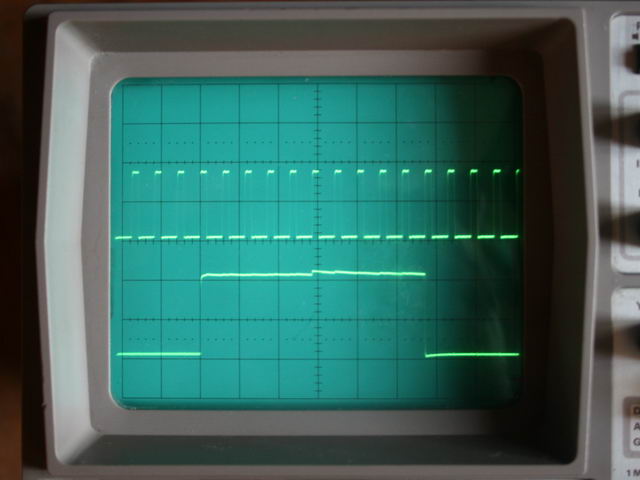

The editing window of the Abel file with the test program used here, a 2, 4, 8, 10, 20, and 40 digital divider. This give 20MHz, 10 MHz, 5 MHz, 4 MHz, 2 MHz and 1 MHz from a 40 MHz clock input.

Source

The pinout definition with the "Constraints Editor".

Simulation

Viewing of the test vectors.

Programming

You will find easily on the Lattice web site, the scheme for a parallel PC programmer.

Here with a small interface for a Labdec breadboard.

Programming

Parameters window for the programming ispVM programming tool from Lattice.

The strange address is coming from the PCMCIA interface I use on my laptop.

Test

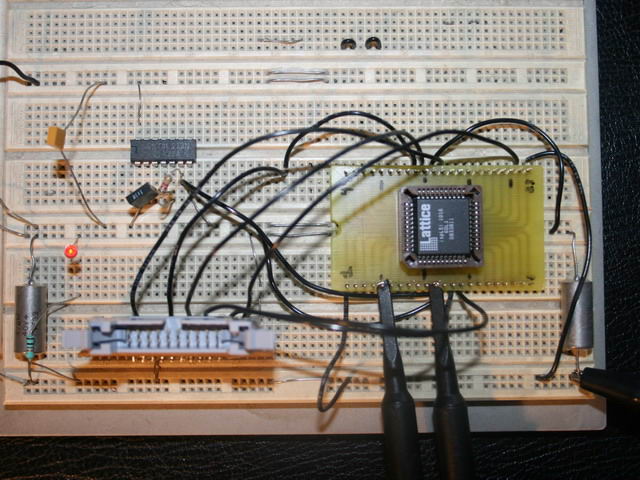

The test on a labdec breadboard using a PLCC 44 adapter.

Test

Result on a scope with the input clock on the top and the divide by 20 on the bottom.