Interface ispLSI1016

Une question, un problème ou une suggestion, n'hésitez pas : un petit mail

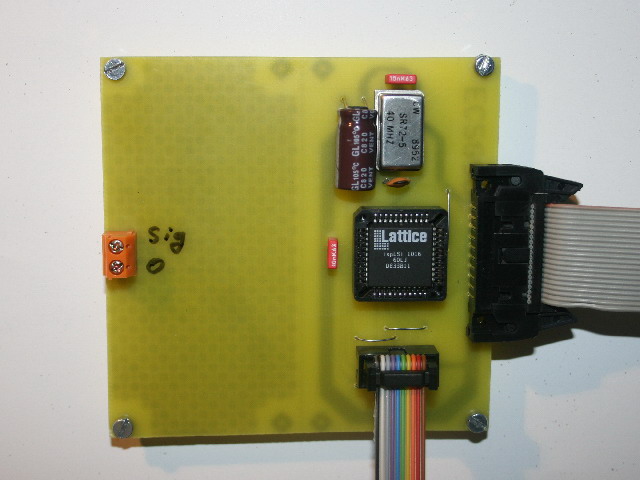

Interface ispLSI1016

Carte permettant l'interfacage entre un bus Peri1 et un FPGA ispLSI1016 de Lattice.

La carte inclut un oscilateur pour l'horloge de l'ispLSI ainsi que toute une zone de prototypage.

Schéma

Juste 2 composants :

- L'ispLSI1016,

- Un oscilateur optionnel pour l'ispLSI1016.

Et 2 connecteurs, celui du bus Peri1 et celui de la programmation de l'ispLSI.

Typon

Le typon de la carte. Toute la partie gauche est une grande zone de prototypage.

Cliquer sur l'image pour faire apparaitre le typon en pleine résolution (92 ko).

La platine fait 4 x 4 pouces (102 x 102 mm) et la résolution du fichier est de 600 dpi (avec la zone de prototypage).

Implantation

L'implantation des différents composants de la platine.

6 straps pour éviter une carte double face dont 2 en dessous de l'ispLSI1016.

Firmware de l'ispLSI

Vous trouverez ici (18 ko) la partie ispLSI d'un programme de test vérifiant que les opérations principales d'entrées/sorties fonctionnent.

Programme de test

Vous trouverez ici (22 ko) la partie PC d'un programme de test de la carte via l'interface USB2Peri1.

Si tout se passe bien, vous pourez voir quelque chose comme cet écran ou un diagnostique d'erreur dans le cas contraire.